By David Herres

Complementary metal-oxide semiconductor (CMOS) is a highly successful strategy for combining complementary and symmetrical pairs of p-type and n-type MOSFETs to create logic functions. A CMOS transistor pair is typically a building block for integrated circuits. Among its many applications are image sensors in digital cameras, data converters and transceivers.

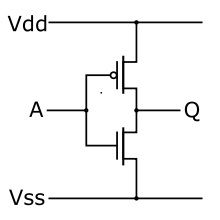

In a common form, one p-type MOSFET and one n-type MOSFET are wired together to make a complementary and symmetrical pair. The defining quality of a p-type MOSFET is that there is low resistance between the source and drain when a low voltage is applied at the gate. Conversely, in an n-Type MOSFET, there is high resistance between source and drain when the gate voltage is low, and low resistance between the source and drain when the gate voltage is high.

By connecting both gates together and both drains together, as shown in the schematic, the two opposite types of MOSFET’s work in concert. When high voltage is applied to the gates, the n-type MOSFET will conduct and the P-type MOSFET will not conduct. A low voltage on the gates will cause the opposite, i.e. the n-type MOSFET will not conduct and the p-type will.

A CMOS gate is composed of two opposite type MOSFETs. CMOS technology can also be found in analog uses such as op amps and mixed-signal analog/digital circuits.

The upshot of all this is that one of the two MOSFETs is always off. And because they are in series with respect to the power supply, the combination consumes little power. (The interesting thing about a CMOS pair is that they are in series with respect to the power supply and in parallel with respect to the signal.) The two devices in series do not conduct, except briefly during transitions. At these moments, there is a short high-intensity spike. It may create a problem if not accounted for and mitigated. RF interference may adversely affect nearby electronic equipment and there can be power quality issues.

Despite all this, CMOS technology has been exactly the right solution at the right time. Its average power consumption, heat dissipation and temperature rise are comparatively low, permitting massive integration of devices on a single small crystalline silicon substrate. This achievement fit the bill to satisfy ongoing needs for increased bandwidth and high-speed connectivity.

Leave a Reply

You must be logged in to post a comment.