Keysight Technologies, Inc. introduced the DDR Bus Simulator; the industry’s first tool to generate accurate Bit-Error-Rate (BER) contours for the JEDEC DDR memory bus specification.

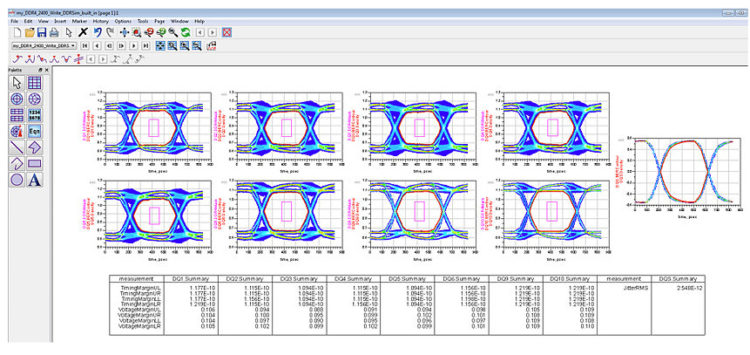

The software product, which is available as a new option for Advanced Design System (ADS) 2014.11 from Keysight EEsof EDA, quickly and accurately calculates DQ and DQS eye probability density distributions and BER contours for memory interfaces. The simulator achieves this through use of statistical simulation, meaning no lengthy or time-consuming bit pattern is needed. Instead, it constructs the eye diagram from the transmitter, channel and receiver impulse responses, and from the stochastic properties of a conceptually infinite non-repeating bit pattern. Previously available tools constructed eye diagrams using precarious dual-Dirac extrapolation of a limited bit pattern from either a SPICE-like or convolutional channel simulation.

“Individual simulations are both fast and accurate, allowing designers to run in batch mode and quickly explore the design space,” says Colin Warwick, product manager for signal integrity tools at Keysight EEsof EDA. “In addition, we offer DDR Bus Simulator Distributed Computing 8-pack licenses so users can farm out their parameter sweeps to a compute cluster for an even shorter time-to-answer.”

The ADS DDR Bus Simulator offers rigorous DQ and DQS eye calculations to arbitrarily low BER levels, including the 1E-16 contour specified by JEDEC. The simulator accounts for crosstalk and asymmetry between rising and falling transition times, and provides comprehensive timing and voltage margins between the contour and DDR4 receive mask specification.

The ADS DDR Bus Simulator allows for three IC model types: built-in, IBIS or circuit models; all of which can be “mixed and matched” in a schematic. The built-in driver and receiver contain de-emphasis and continuous-time linear equalization capabilities, respectively.

U.S. Pricing and Availability

The ADS DDR Bus Simulator and DDR Bus Simulator Distributed Computing 8-pack will be available this winter as part of the ADS 2014.11 release. Pricing is dependent on the exact configuration desired.

Keysight

www.Keysight.com

Leave a Reply

You must be logged in to post a comment.