PAM4 modulation boosts throughput but adds test challenges.

The Peripheral Component Interface (PCI) emerged in the 1990s as a parallel bus for connecting computer mainboards and peripheral devices. In 2003, a serial version called PCI Express (PCIe) debuted, with generation 1 offering a transfer rate of 2.5 GT/s. Over the past 20 years, successive generations have offered increasing throughput rates (Table 1), with gen 6, released in 2022 by the PCI Special Interest Group (PCI-SIG), offering a 64-GT/s transfer rate. The PCIe standard defines multiple lane configurations, including x1 for a single lane, x4 for four lanes, x8 for eight lanes, and x16 for 16 lanes, with each lane consisting of a transmit/receive signal pair. An x16 implementation of PCIe 6 offers a throughput approaching 128 GB/s in each direction.

| Version | Year | Signaling method | Per-lane Transfer Rate (GT/s) |

| 1.0 | 2003 | NRZ | 2.5 |

| 2.0 | 2007 | NRZ | 5.0 |

| 3.0 | 2010 | NRZ | 8.0 |

| 4.0 | 2017 | NRZ | 16.0 |

| 5.0 | 2019 | NRZ | 32.0 |

| 6.0 | 2022 | PAM4 | 64.0 |

Table 1. PCIe Versions

Twenty years old — does this standard have a future?

Yes. Gen 6 has a feature that we’ll discuss shortly that will help propel the standard forward. Indeed, the PCI-SIG in June 2023 released findings from ABI Research showing that the total addressable market (TAM) for PCIe is growing at a compound annual growth rate (CAGR) of 14% from 2022 to 2027. PCIe has always been strong in the datacenter, but the PCI-SIG sees the highest growth opportunities in the automotive and network-edge verticals—markets that ABI Research expects will grow at a CAGR of 38% through 2027. And PCIe innovation isn’t stopping at gen 6. PCI-SIG expects to release the PCIe 7 standard in 2025 with a 128-GT/s raw bit rate.

What are the signaling methods mentioned in Table 1?

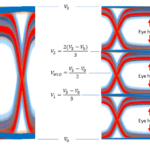

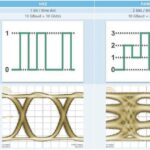

PCIe generations 1 through 5 use non-return-to-zero (NRZ) signaling, which carries one bit per unit interval (UI), as shown on the left in the Figure 1 eye diagrams. (We discussed the UI and eye diagram in earlier posts on jitter.) PCIe version 6 retains the 16-GHz Nyquist frequency of version 5, but it employs four-level pulse amplitude modulation (PAM4), shown on the right of Figure 1. PAM4, the new feature I alluded to earlier, carries two bits per UI, thereby doubling the throughput at the same Nyquist frequency. The PAM4 waveform, however, has three stacked eyes in the vertical space of one eye of the NRZ waveform, thereby degrading signal-to-noise ratio. Note that for the 16-GHz Nyquist frequency, one UI equals 31.25 ps (one half of one cycle period).

How does this work if we want to use PAM4 to send a specific sequence — say, 00 01 10 11?

Here’s how to send the decimal sequence zero, one, two, three in binary format over PAM4. By way of comparison, the top bit stream in Figure 2 shows your sequence transferred in NRZ. Note that the zero point on the vertical axis refers to the logic state — not zero volts. With PCIe, the actual voltage swing is plus or minus several hundred millivolts. It takes eight UIs to transfer your eight-bit sequence using NRZ.

Now look at the PAM4 representation on the bottom of Figure 2. The sequence 00 gets transferred in the first UI, and 01 gets transferred in the second. Then things get a bit interesting — or maybe two bits interesting. Counting up incrementally in binary, during the transition from decimal one (binary 01) to decimal two (binary 10), both binary bits flip. This double flip can induce errors and complicate error correction. To avoid these pitfalls, many PAM4 implementations, including PCIe 6, employ the reflected binary code (RBC), also known as the Gray code, as shown in Table 2, where the red numerals indicate the bits that flip as the count increments.

| Decimal number |

Binary code | Gray code |

| 0 | 00 | 00 |

| 1 | 01 | 01 |

| 2 | 10 | 11 |

| 3 | 11 | 10 |

| 0 | 00 | 00 |

| … | … | … |

Table 2. Gray Code

Consequently, the fifth and sixth bits in your sequence (1 and 0, respectively) correspond to binary 11. The final two bits (1 and 1) correspond to binary 10. As shown by the red Gray code digits in Figure 2, we have completed the transfer of your sequence in just four UIs.

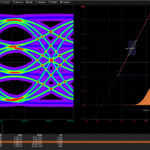

What tests do we need to perform on PCIe 6 products?

PCIe 6 requires extensive tests of transmitters, receivers, and interconnects, with measurements of parameters ranging from signal-to-noise and distortion ratio (SNDR) to inter-symbol interference (ISI). Products available for PCIe test extend from design and simulation software suites to oscilloscopes, bit error ratio testers (BERTs), vector network analyzers, and protocol analyzers. We will look at some specific tests in part 2.

Where can I learn more now?

Intel has a paper on PAM4 signaling fundamentals; click here and the PDF will download. In addition, the PCI-SIG has a white paper on PCIe 6. You might also want to plan to attend an event such as the PCI-SIG Compliance Workshop July 31 to August 4, 2023, in Burlingame, CA.

Leave a Reply

You must be logged in to post a comment.